Difference between revisions of "Template:OpenEP4CE10-C User Manual"

| Line 119: | Line 119: | ||

:4. Back to the Nios II IDE | :4. Back to the Nios II IDE | ||

::1) Download the Nios II processor to the FPGA, select"Tools->Quaters II Programmer" to download the sof file. | ::1) Download the Nios II processor to the FPGA, select"Tools->Quaters II Programmer" to download the sof file. | ||

| − | ::2) Run the Nios II project (right click the makefile, select "Run ->Run As->2 Nios II Hardware", it may takes several minutes). When download completed, the demo code should starts to run automatically. | + | ::2) Run the Nios II project (right click the makefile, select "Run ->Run As->2 Nios II Hardware", it may takes several minutes). When download completed, the demo code should starts to run automatically.<br/> |

| − | <br/> | + | == Quick Start == |

| − | {{Altera-Test- | + | ::All the following demo require power supply. Verilog, VHDL and NIOS are used in the following demos, please download the corresponding one.<br /> |

| + | ::An OpenEP4CE10-C development board is used for demonstration, other Altera boards are similar to it. If there are differences on any example, they will be special explained. | ||

| + | |||

| + | === Light Up LEDs === | ||

| + | <br /> | ||

| + | {| class="tabSty_1" width="96%" border="1" | ||

| + | |- | ||

| + | ! | <p>Language</p> | ||

| + | ! | <p>Verilog</p> | ||

| + | ! | <p>VHDL</p> | ||

| + | ! | <p>Nios II C</p> | ||

| + | |- | ||

| + | |<p align="center"> '''Sample Program Name'''</p> | ||

| + | | colspan="2" | <p align="center">LED</p> | ||

| + | | <p align="center">LED_hello_world</p> | ||

| + | |- | ||

| + | |<p align="center"> '''Steps'''</p> | ||

| + | | colspan="3" | | ||

| + | #Connect the "SDRAM Board" to the SDRAM interface (required only when the Nios II is launched) | ||

| + | #Download the program | ||

| + | |- | ||

| + | |<p align="center"> '''Phenomena'''</p> | ||

| + | | colspan="2" | | ||

| + | *Onboard 4 LEDs flow from the left to the right.<br /> | ||

| + | | | ||

| + | *LED keeps blinking; | ||

| + | *The NOIS II project Console tab shows "hello_world" | ||

| + | |- | ||

| + | | <p align="center"> '''实验视频'''</p> | ||

| + | | <p align="center">[[File:video-logo.png|30px|link=Altera-Test-1-LED-Verilog ]] </p> | ||

| + | | <p align="center">[[File:video-logo.png|30px|link=Altera-Test-1-LED-VHDL ]] </p> | ||

| + | | <p align="center">[[File:video-logo.png|30px|link=Altera-Test-1-LED-NIOS]] </p> | ||

| + | |} | ||

| + | <br /> | ||

| + | |||

| + | === 控制摇杆JOYSTICK实验 === | ||

| + | <br /> | ||

| + | {| class="tabSty_1" width="96%" border="1" | ||

| + | |- | ||

| + | ! | | ||

| + | Language | ||

| + | |||

| + | ! | | ||

| + | Verilog | ||

| + | |||

| + | ! | | ||

| + | VHDL | ||

| + | |||

| + | ! | | ||

| + | Nios II C | ||

| + | |||

| + | |- | ||

| + | | <p style="text-align: center;">'''Sample Program Name'''</p> | ||

| + | | colspan="3" | <p style="text-align: center;"><span style="color: rgb(0, 0, 0); font-family: sans-serif; line-height: 19.200000762939453px;">JOYSTICK</span></p> | ||

| + | |- | ||

| + | | <p style="text-align: center;">'''Steps'''</p> | ||

| + | | colspan="3" | | ||

| + | #跳上底板上JOYSTICK_JMP处的跳线帽 | ||

| + | #将SDRAM Board插入SDRAM接口(运行Nios II才用插) | ||

| + | #<span style="color: rgb(0, 0, 0); font-family: sans-serif; line-height: 19.200000762939453px;">Download the program</span> | ||

| + | |- | ||

| + | | <p style="text-align: center;">'''Phenomena'''</p> | ||

| + | | colspan="3" | | ||

| + | *<span style="color: rgb(0, 0, 0); font-family: sans-serif; line-height: 19.200000762939453px;">拨动JOYSTICK摇杆的不用方向,可以看到L1~L4四个LED会有对应的亮灭变化。</span> | ||

| + | |- | ||

| + | | <p align="center"> '''实验视频'''</p> | ||

| + | | <p align="center">[[File:video-logo.png|30px|link=Altera-Test-2-JOYSTICK-Verilog]] </p> | ||

| + | | <p align="center">[[File:video-logo.png|30px|link=Altera-Test-2-JOYSTICK-VHDL]] </p> | ||

| + | | <p align="center">[[File:video-logo.png|30px|link=Altera-Test-2-JOYSTICK-NIOS]] </p> | ||

| + | |} | ||

| + | <br /> | ||

| + | |||

| + | === 8 Push Buttons按键实验 === | ||

| + | <br /> | ||

| + | {| class="tabSty_1" width="96%" border="1" | ||

| + | |- | ||

| + | ! | ||

| + | Language | ||

| + | |||

| + | ! | ||

| + | Verilog | ||

| + | |||

| + | ! | ||

| + | VHDL | ||

| + | |||

| + | ! | ||

| + | Nios II C | ||

| + | |||

| + | |- | ||

| + | | <p style="text-align: center;">'''Sample Program Name'''</p> | ||

| + | | colspan="2" | <p style="text-align: center;"><span style="color: rgb(0, 0, 0); font-family: sans-serif; line-height: 19.200000762939453px;">8 Push Buttons</span></p> | ||

| + | | style="text-align: center;" | <font color="#000000" face="sans-serif"><span style="line-height: 19.200000762939453px;">——</span></font> | ||

| + | |- | ||

| + | | <p style="text-align: center;">'''Steps'''</p> | ||

| + | | colspan="2" | | ||

| + | #将8 Push Buttons连接到8I/Os_1接口 | ||

| + | #<span style="color: rgb(0, 0, 0); font-family: sans-serif; line-height: 19.200000762939453px;">Download the program</span> | ||

| + | |||

| + | | | ||

| + | |- | ||

| + | | <p style="text-align: center;">'''Phenomena'''</p> | ||

| + | | colspan="2" | | ||

| + | *<span style="color: rgb(0, 0, 0); font-family: sans-serif; line-height: 19.200000762939453px;">按下8 Push Buttons模块上的按键,核心板上的LED会有相应的显示。</span> | ||

| + | |||

| + | | | ||

| + | |- | ||

| + | | <p align="center"> '''实验视频'''</p> | ||

| + | | <p align="center">[[File:video-logo.png|30px|link=Altera-Test-3-8-Push-Buttons-Verilog]] </p> | ||

| + | | <p align="center">[[File:video-logo.png|30px|link=Altera-Test-3-8-Push-Buttons-VHDL]] </p> | ||

| + | | <p align="center"> -- </p> | ||

| + | |} | ||

| + | <br /> | ||

| + | |||

| + | === 8 LEG LED Board数码管实验 === | ||

| + | <br /> | ||

| + | {| class="tabSty_1" width="96%" border="1" | ||

| + | |- | ||

| + | ! | | ||

| + | Language | ||

| + | |||

| + | ! | | ||

| + | Verilog | ||

| + | |||

| + | ! | | ||

| + | VHDL | ||

| + | |||

| + | ! | | ||

| + | Nios II C | ||

| + | |||

| + | |- | ||

| + | | <p style="text-align: center;">'''Sample Program Name'''</p> | ||

| + | | colspan="2" | <p style="text-align: center;"><span style="color: rgb(0, 0, 0); font-family: sans-serif; line-height: 19.200000762939453px;">8 SEG LED Board</span></p> | ||

| + | | style="text-align: center;" | —— | ||

| + | |- | ||

| + | | <p style="text-align: center;">'''Steps'''</p> | ||

| + | | colspan="2" | | ||

| + | #8 LEG LED Board接入16I/Os_2接口 | ||

| + | #<span style="color: rgb(0, 0, 0); font-family: sans-serif; line-height: 19.200000762939453px;">Download the program</span> | ||

| + | |||

| + | | | ||

| + | |- | ||

| + | | <p style="text-align: center;">'''Phenomena'''</p> | ||

| + | | colspan="2" | | ||

| + | *<span style="color: rgb(0, 0, 0); font-family: sans-serif; line-height: 19.200000762939453px;">8 LEG LED Board模块上的4个数码管会自动显示0~E等字符</span> | ||

| + | |||

| + | | | ||

| + | |- | ||

| + | | <p align="center"> '''实验视频'''</p> | ||

| + | | <p align="center">[[File:video-logo.png|30px|link=Altera-Test-4-8-SEG-LED-Board-Verilog]] </p> | ||

| + | | <p align="center">[[File:video-logo.png|30px|link=Altera-Test-4-8-SEG-LED-Board-VHDL]] </p> | ||

| + | | <p align="center"> -- </p> | ||

| + | |} | ||

| + | <br /> | ||

| + | |||

| + | === 4x4 Keypad矩阵键盘控制数码管实验 === | ||

| + | <br /> | ||

| + | {| class="tabSty_1" width="96%" border="1" | ||

| + | |- | ||

| + | ! | | ||

| + | Language | ||

| + | |||

| + | ! | Verilog | ||

| + | ! | VHDL | ||

| + | ! | Nios II C | ||

| + | |- | ||

| + | | style="text-align: center;" | | ||

| + | '''Sample Program Name''' | ||

| + | |||

| + | | colspan="3" style="text-align: center;" | <span style="color: rgb(0, 0, 0); font-family: sans-serif; line-height: 19.200000762939453px;">4x4 Keypad</span> | ||

| + | |- | ||

| + | | style="text-align: center;" | | ||

| + | '''Steps''' | ||

| + | |||

| + | | <ol style="padding-right: 0px; padding-left: 0px; line-height: 19.200000762939453px; margin: 0.3em 0px 0px 3.2em; list-style-image: none; color: rgb(0, 0, 0); font-family: sans-serif;"> | ||

| + | <li>将4x4 Keypad连接到8I/Os_1接口上</li> | ||

| + | <li>Download the program</li> | ||

| + | </ol> | ||

| + | |||

| + | | <ol style="line-height: 19.200000762939453px; margin: 0.3em 0px 0px 3.2em; padding-right: 0px; padding-left: 0px; list-style-image: none; color: rgb(0, 0, 0); font-family: sans-serif;"> | ||

| + | <li>将4x4 Keypad连接到8I/Os_1接口上</li> | ||

| + | <li>将8 SEG LED Board连接到16I/Os_2接口上</li> | ||

| + | <li><span style="color: rgb(0, 0, 0); font-family: sans-serif; line-height: 19.200000762939453px;">Download the program</span></li> | ||

| + | </ol> | ||

| + | |||

| + | | <ol style="line-height: 19.200000762939453px; margin: 0.3em 0px 0px 3.2em; padding-right: 0px; padding-left: 0px; list-style-image: none; color: rgb(0, 0, 0); font-family: sans-serif;"> | ||

| + | <li>将4x4 Keypad连接到8I/Os_1接口上</li> | ||

| + | <li>将SDRAM Board插入SDRAM接口上</li> | ||

| + | <li>Download the program</li> | ||

| + | |- | ||

| + | | style="text-align: center;" | | ||

| + | '''Phenomena''' | ||

| + | |||

| + | | | ||

| + | *<span style="color: rgb(0, 0, 0); font-family: sans-serif; line-height: 19.200000762939453px;">4x4 Keypad控制的是核心板的LED灯</span> | ||

| + | |||

| + | | | ||

| + | * <span style="color: rgb(0, 0, 0); font-family: sans-serif; line-height: 19.200000762939453px;">4x4 Keypad控制的是数码管的显示</span> | ||

| + | |||

| + | | | ||

| + | *<span style="color: rgb(0, 0, 0); font-family: sans-serif; line-height: 19.200000762939453px;">4x4 Keypad控制的是核心板的LED灯</span> | ||

| + | |||

| + | |- | ||

| + | | <p align="center"> '''实验视频'''</p> | ||

| + | | <p align="center">[[File:video-logo.png|30px|link=Altera-Test-5-4x4-Keypad-Verilog]] </p> | ||

| + | | <p align="center">[[File:video-logo.png|30px|link=Altera-Test-5-4x4-Keypad-VHDL]] </p> | ||

| + | | <p align="center">[[File:video-logo.png|30px|link=Altera-Test-5-4x4-Keypad-NIOS]] </p> | ||

| + | |} | ||

| + | |||

| + | === DS18B20温度传感器实验 === | ||

| + | <br /> | ||

| + | {| class="tabSty_1" width="96%" border="1" | ||

| + | |- | ||

| + | ! | | ||

| + | Language | ||

| + | |||

| + | ! | Verilog | ||

| + | ! | VHDL | ||

| + | ! | Nios II C | ||

| + | |- | ||

| + | |<p align="center"> '''Sample Program Name'''</p> | ||

| + | | colspan="3" style="text-align: center;" | <span style="color: rgb(0, 0, 0); font-family: sans-serif; line-height: 19.200000762939453px;">DS18B20</span> | ||

| + | |- | ||

| + | | style="text-align: center;" | | ||

| + | '''Steps''' | ||

| + | |||

| + | | <ol style="line-height: 19.200000762939453px; margin: 0.3em 0px 0px 3.2em; padding-right: 0px; padding-left: 0px; list-style-image: none; color: rgb(0, 0, 0); font-family: sans-serif;"> | ||

| + | <li>将DS18B20+连接到1-WIRE接口上</li> | ||

| + | <li>跳上1-WIREJMP跳线帽</li> | ||

| + | <li>将8 SEG LED Board插入16I/Os_2</li> | ||

| + | <li><span style="color: rgb(0, 0, 0); font-family: sans-serif; line-height: 19.200000762939453px;">Download the program</span></li> | ||

| + | </ol> | ||

| + | |||

| + | | <ol style="line-height: 19.200000762939453px; margin: 0.3em 0px 0px 3.2em; padding-right: 0px; padding-left: 0px; list-style-image: none; color: rgb(0, 0, 0); font-family: sans-serif;"> | ||

| + | <li>将DS18B20+连接到1-WIRE接口上</li> | ||

| + | <li>跳上1-WIREJMP跳线帽</li> | ||

| + | <li><span style="color: rgb(0, 0, 0); font-family: sans-serif; line-height: 19.200000762939453px;">将LCD1602插入LCD1602接口</span></li> | ||

| + | <li><span style="color: rgb(0, 0, 0); font-family: sans-serif; line-height: 19.200000762939453px;">Download the program</span></li> | ||

| + | </ol> | ||

| + | |||

| + | | <ol style="line-height: 19.200000762939453px; margin: 0.3em 0px 0px 3.2em; padding-right: 0px; padding-left: 0px; list-style-image: none; color: rgb(0, 0, 0); font-family: sans-serif;"> | ||

| + | <li>将DS18B20+连接到1-WIRE接口上</li> | ||

| + | <li>跳上1-WIREJMP跳线帽</li> | ||

| + | <li>将SDRAM Board插入SDRAM接口</li> | ||

| + | <li>重启板子电源</li> | ||

| + | |- | ||

| + | | style="text-align: center;" | | ||

| + | '''Phenomena''' | ||

| + | |||

| + | | | ||

| + | *LCD1602显示温度 | ||

| + | | | ||

| + | *数码管显示温度 | ||

| + | | | ||

| + | *Nios II软件的Console栏显示温度 | ||

| + | |} | ||

| + | |||

| + | [[File:Altera-DS18B20-Verilog.jpg|300px]] | ||

| + | [[File:Altera-DS18B20-VHDL.jpg|300px]] | ||

| + | |||

| + | === 蜂鸣器实验 === | ||

| + | <br /> | ||

| + | {| class="tabSty_1" width="96%" border="1" | ||

| + | |- | ||

| + | ! | | ||

| + | <span style="font-weight: normal;">Language</span> | ||

| + | |||

| + | ! | | ||

| + | <span style="font-weight: normal;">Verilog</span> | ||

| + | |||

| + | ! | | ||

| + | <span style="font-weight: normal;">VHDL</span> | ||

| + | |||

| + | ! | | ||

| + | <span style="font-weight: normal;">Nios II C</span> | ||

| + | |||

| + | |- | ||

| + | | <p style="text-align: center;">'''Sample Program Name'''</p> | ||

| + | | colspan="2" | <p style="text-align: center;">Buzzer/PWM</p> | ||

| + | | style="text-align: center;" | —— | ||

| + | |- | ||

| + | | <p style="text-align: center;">'''Steps'''</p> | ||

| + | | colspan="2" | | ||

| + | #将Buzzer处跳线帽接上 | ||

| + | #Download the program | ||

| + | |||

| + | | | ||

| + | |- | ||

| + | | <p style="text-align: center;">'''Phenomena'''</p> | ||

| + | | colspan="2" | | ||

| + | *蜂鸣器响 | ||

| + | |||

| + | | | ||

| + | |} | ||

| + | |||

| + | === PS/2键盘实验 === | ||

| + | <br /> | ||

| + | {| class="tabSty_1" width="96%" border="1" | ||

| + | |- | ||

| + | ! | | ||

| + | <span style="font-weight: normal;">Language</span> | ||

| + | |||

| + | ! | <span style="font-weight: normal;">Verilog</span> | ||

| + | ! | <span style="font-weight: normal;">VHDL</span> | ||

| + | ! | <span style="font-weight: normal;">Nios II C</span> | ||

| + | |- | ||

| + | | style="text-align: center;" | | ||

| + | '''Sample Program Name''' | ||

| + | |||

| + | | colspan="3" style="text-align: center;" | PS2 | ||

| + | |- | ||

| + | | style="text-align: center;" | | ||

| + | '''Steps''' | ||

| + | |||

| + | | colspan="2" | | ||

| + | #将VGA PS2 Board插入16I/Os_2,接上键盘 | ||

| + | #将LCD1602插入LCD1602接口 | ||

| + | #Download the program | ||

| + | |||

| + | | | ||

| + | #将VGA PS2 Board插入16I/Os_2,接上键盘 | ||

| + | #将SDRAM Board插入SDRAM接口 | ||

| + | #Download the program | ||

| + | #重启板子电源 | ||

| + | |- | ||

| + | | style="text-align: center;" | | ||

| + | '''Phenomena''' | ||

| + | |||

| + | | colspan="2" | | ||

| + | *键盘值在lLCD602上显示 | ||

| + | |||

| + | | | ||

| + | *按键盘对应ASIC码在Nios II软件的Console栏显示 | ||

| + | |- | ||

| + | | <p align="center"> '''实验视频'''</p> | ||

| + | | colspan="2" | <p align="center">[[File:video-logo.png|30px|link=Altera-Test-8-PS2-Verilog_VHDL]] </p> | ||

| + | | <p align="center">[[File:video-logo.png|30px|link=Altera-Test-8-PS2-NIOS]] </p> | ||

| + | |} | ||

| + | <br /> | ||

| + | |||

| + | === VGA显示实验 === | ||

| + | <br /> | ||

| + | {| class="tabSty_1" width="96%" border="1" | ||

| + | |- | ||

| + | ! | | ||

| + | <span style="font-weight: normal;">Language</span> | ||

| + | |||

| + | ! | <span style="font-weight: normal;">Verilog</span> | ||

| + | ! | <span style="font-weight: normal;">VHDL</span> | ||

| + | ! | <span style="font-weight: normal;">Nios II C</span> | ||

| + | |- | ||

| + | | style="text-align: center;" | | ||

| + | '''Sample Program Name''' | ||

| + | |||

| + | | style="text-align: center;" | VGA_color | ||

| + | | style="text-align: center;" | VGA | ||

| + | | style="text-align: center;" | —— | ||

| + | |- | ||

| + | | style="text-align: center;" | | ||

| + | '''Steps''' | ||

| + | |||

| + | | colspan="2" | | ||

| + | #将VGA PS2 Board插入16I/Os_2 | ||

| + | #接上VGA电脑显示器 | ||

| + | #Download the program | ||

| + | |||

| + | | | ||

| + | |- | ||

| + | | style="text-align: center;" | | ||

| + | '''Phenomena''' | ||

| + | |||

| + | | colspan="2" | | ||

| + | *VGA显示器显示 | ||

| + | |||

| + | | | ||

| + | |- | ||

| + | | <p align="center"> '''实验视频'''</p> | ||

| + | | <p align="center">[[File:video-logo.png|30px|link=Altera-Test-9-VGA_color-Verilog]] </p> | ||

| + | | <p align="center">[[File:video-logo.png|30px|link=Altera-Test-9-VGA-VHDL]] </p> | ||

| + | | <p align="center"> -- </p> | ||

| + | |||

| + | |} | ||

| + | |||

| + | === 字符LCD1602实验 === | ||

| + | <br /> | ||

| + | {| class="tabSty_1" width="96%" border="1" | ||

| + | |- | ||

| + | ! | | ||

| + | <span style="font-weight: normal;">Language</span> | ||

| + | |||

| + | ! | | ||

| + | <span style="font-weight: normal;">Verilog</span> | ||

| + | |||

| + | ! | | ||

| + | <span style="font-weight: normal;">VHDL</span> | ||

| + | |||

| + | ! | | ||

| + | <span style="font-weight: normal;">Nios II C</span> | ||

| + | |||

| + | |- | ||

| + | | <p style="text-align: center;">'''Sample Program Name'''</p> | ||

| + | | colspan="2" | <p style="text-align: center;">LCD1602</p> | ||

| + | | style="text-align: center;" | —— | ||

| + | |- | ||

| + | | <p style="text-align: center;">'''Steps'''</p> | ||

| + | | colspan="2" | | ||

| + | #将LCD1602插入LCD1602接口 | ||

| + | #Download the program | ||

| + | |||

| + | | | ||

| + | |- | ||

| + | | <p style="text-align: center;">'''Phenomena'''</p> | ||

| + | | colspan="2" | | ||

| + | *1602显示画面 | ||

| + | |||

| + | | | ||

| + | |} | ||

| + | <gallery> | ||

| + | |||

| + | File:Altera-LCD1602-Verilog.jpg | ||

| + | File:Altera-LCD1602-VHDL-2.jpg | ||

| + | File:Altera-LCD1602-VHDL-1.jpg | ||

| + | File:Altera-LCD1602-VHDL-3.jpg | ||

| + | |||

| + | </gallery> | ||

| + | |||

| + | === 点阵LCD12864实验 === | ||

| + | <br /> | ||

| + | {| class="tabSty_1" width="96%" border="1" | ||

| + | |- | ||

| + | ! | | ||

| + | <span style="font-weight: normal;">Language</span> | ||

| + | |||

| + | ! | <span style="font-weight: normal;">Verilog</span> | ||

| + | ! | <span style="font-weight: normal;">VHDL</span> | ||

| + | ! | <span style="font-weight: normal;">Nios II C</span> | ||

| + | |- | ||

| + | | style="text-align: center;" | | ||

| + | '''Sample Program Name''' | ||

| + | |||

| + | | style="text-align: center;" | LCD12864 | ||

| + | | style="text-align: center;" | —— | ||

| + | | style="text-align: center;" | —— | ||

| + | |- | ||

| + | | style="text-align: center;" | | ||

| + | '''Steps''' | ||

| + | |||

| + | | | ||

| + | # 将LCD12864插到开发板的LCD接口上 | ||

| + | #Download the program | ||

| + | |||

| + | | | ||

| + | | | ||

| + | |- | ||

| + | | style="text-align: center;" | | ||

| + | '''Phenomena''' | ||

| + | |||

| + | | | ||

| + | * LCD12864显示画面 | ||

| + | |||

| + | | | ||

| + | | | ||

| + | |} | ||

| + | [[File:Altera-LCD12864-Verilog.jpg|400px]] | ||

| + | |||

| + | === 3.2寸LCD屏显示触摸实验 === | ||

| + | <br /> | ||

| + | {| class="tabSty_1" width="96%" border="1" | ||

| + | |- | ||

| + | ! | ||

| + | <span style="font-weight: normal;">Language</span> | ||

| + | |||

| + | ! <span style="font-weight: normal;">Verilog</span> | ||

| + | ! <span style="font-weight: normal;">VHDL</span> | ||

| + | ! <span style="font-weight: normal;">Nios II C</span> | ||

| + | |- | ||

| + | | style="text-align: center;" | | ||

| + | '''Sample Program Name''' | ||

| + | |||

| + | | style="text-align: center;" | —— | ||

| + | | style="text-align: center;" | —— | ||

| + | | style="text-align: center;" | LCD32 | ||

| + | |- | ||

| + | | style="text-align: center;" | | ||

| + | '''Steps''' | ||

| + | |||

| + | | | ||

| + | | | ||

| + | | | ||

| + | # 将3.2inch 320x240 Touch LCD通过3.2 inch LCD Adapter(B)转接块插入32I/Os_2接口 | ||

| + | #将SDRAM Board插入SDRAM接口 | ||

| + | #Download the program | ||

| + | #下载完成后重启电源 | ||

| + | |||

| + | |- | ||

| + | | style="text-align: center;" | | ||

| + | '''Phenomena''' | ||

| + | |||

| + | | | ||

| + | | | ||

| + | | | ||

| + | * 3.2inch 320x240 Touch LCD 显示并且可以触摸 | ||

| + | |||

| + | |} | ||

| + | |||

| + | === USB通信实验 === | ||

| + | <br /> | ||

| + | {| class="tabSty_1" width="96%" border="1" | ||

| + | |- | ||

| + | ! | | ||

| + | <span style="font-weight: normal;">Language</span> | ||

| + | |||

| + | ! | <span style="font-weight: normal;">Verilog</span> | ||

| + | ! | <span style="font-weight: normal;">VHDL</span> | ||

| + | ! | <span style="font-weight: normal;">Nios II C</span> | ||

| + | |- | ||

| + | | style="text-align: center;" | | ||

| + | '''Sample Program Name''' | ||

| + | |||

| + | | style="text-align: center;" | —— | ||

| + | | style="text-align: center;" | USB | ||

| + | | style="text-align: center;" | —— | ||

| + | |- | ||

| + | | style="text-align: center;" | | ||

| + | '''Steps''' | ||

| + | |||

| + | | | ||

| + | | | ||

| + | # 将CY7C68013A USB Board插入32I/Os_1接口,并把它的另外一端接到PC机上 | ||

| + | #Download the program | ||

| + | |||

| + | | | ||

| + | |- | ||

| + | | style="text-align: center;" | | ||

| + | '''Phenomena''' | ||

| + | |||

| + | | | ||

| + | |||

| + | |||

| + | | | ||

| + | * 通过上位机USB_LED.exe可以控制开发板上的LED | ||

| + | |||

| + | | | ||

| + | |- | ||

| + | | style="text-align: center;" | | ||

| + | 备注 | ||

| + | |||

| + | | | ||

| + | |||

| + | |||

| + | | | ||

| + | *在使用CY7C68013A USB Board模块前,需要先安装驱动软件:EZ-USB.exe | ||

| + | |||

| + | | | ||

| + | |- | ||

| + | | <p align="center"> '''实验视频'''</p> | ||

| + | | <p align="center"> -- </p> | ||

| + | | <p align="center">[[File:video-logo.png|30px|link=Altera-Test-13-USB-VHDL]] </p> | ||

| + | | <p align="center"> -- </p> | ||

| + | |} | ||

| + | <br /> | ||

| + | |||

| + | === SD-Card实验 === | ||

| + | <br /> | ||

| + | {| class="tabSty_1" width="96%" border="1" | ||

| + | |- | ||

| + | ! | | ||

| + | <span style="font-weight: normal;">Language</span> | ||

| + | |||

| + | ! | <span style="font-weight: normal;">Verilog</span> | ||

| + | ! | <span style="font-weight: normal;">VHDL</span> | ||

| + | ! | <span style="font-weight: normal;">Nios II C</span> | ||

| + | |- | ||

| + | | style="text-align: center;" | | ||

| + | '''Sample Program Name''' | ||

| + | |||

| + | | style="text-align: center;" | —— | ||

| + | | style="text-align: center;" | —— | ||

| + | | style="text-align: center;" | <span style="text-align: center;">SD-Card</span> | ||

| + | |- | ||

| + | | style="text-align: center;" | | ||

| + | '''Steps''' | ||

| + | |||

| + | | | ||

| + | | | ||

| + | | | ||

| + | # 将Micro SD Storage Board插入8I/Os_1 | ||

| + | #·将SDRAM Board插入SDRAM接口 | ||

| + | #Download the program | ||

| + | #重启板子电源 | ||

| + | |||

| + | |- | ||

| + | | style="text-align: center;" | | ||

| + | '''Phenomena''' | ||

| + | |||

| + | | | ||

| + | |||

| + | |||

| + | | | ||

| + | | | ||

| + | * 先在SD卡自己放入文件MESSAGE.TXT,运行程序后,会在SD卡中创建新的文件hello.txt | ||

| + | *在软件的Console栏读出MESSAGE.TXT内的内容 | ||

| + | |||

| + | |} | ||

| + | <br /> | ||

| + | |||

| + | === Ethernet以太网口通信实验 === | ||

| + | <br /> | ||

| + | {| class="tabSty_1" width="96%" border="1" | ||

| + | |- | ||

| + | ! | | ||

| + | <span style="font-weight: normal;">Language</span> | ||

| + | |||

| + | ! | <span style="font-weight: normal;">Verilog</span> | ||

| + | ! | <span style="font-weight: normal;">VHDL</span> | ||

| + | ! | <span style="font-weight: normal;">Nios II C</span> | ||

| + | |- | ||

| + | | style="text-align: center;" | | ||

| + | '''Sample Program Name''' | ||

| + | |||

| + | | style="text-align: center;" | —— | ||

| + | | style="text-align: center;" | —— | ||

| + | | style="text-align: center;" | ENC28J60 | ||

| + | |- | ||

| + | | style="text-align: center;" | | ||

| + | '''Steps''' | ||

| + | |||

| + | | | ||

| + | | | ||

| + | | | ||

| + | # 将ENC28J60 Ethernet Board接入16I/Os_2中 | ||

| + | #把网线一端接入到电脑,另一端接到PC机上 | ||

| + | #Download the program | ||

| + | |||

| + | |- | ||

| + | | style="text-align: center;" | | ||

| + | '''Phenomena''' | ||

| + | |||

| + | | | ||

| + | | | ||

| + | | | ||

| + | * 在IE浏览器上显示信息,可以按照IE浏览器提示操作 | ||

| + | *在Nios II软件的Console栏显示数字 | ||

| + | |||

| + | |} | ||

| + | <br /> | ||

| + | |||

| + | === UART串口通信实验 === | ||

| + | <br /> | ||

| + | {| class="tabSty_1" width="96%" border="1" | ||

| + | |- | ||

| + | ! | | ||

| + | <span style="font-weight: normal;">Language</span> | ||

| + | |||

| + | ! | <span style="font-weight: normal;">Verilog</span> | ||

| + | ! | <span style="font-weight: normal;">VHDL</span> | ||

| + | ! | <span style="font-weight: normal;">Nios II C</span> | ||

| + | |- | ||

| + | | style="text-align: center;" | | ||

| + | '''Sample Program Name''' | ||

| + | |||

| + | | colspan="3" style="text-align: center;" | UART | ||

| + | |- | ||

| + | | style="text-align: center;" | | ||

| + | '''Steps''' | ||

| + | |||

| + | | | ||

| + | # 将RS232 Board插入8I/Os_1,并把它的另外一端接到PC机上 | ||

| + | #Download the program | ||

| + | |||

| + | | | ||

| + | # 将RS232 Board插入8I/Os_1,并把它的另外一端接到PC机上 | ||

| + | #将8 SEG LED Board插入16I/Os_2 | ||

| + | #Download the program | ||

| + | |||

| + | | | ||

| + | # 将RS232 Board插入8I/Os_1,并把它的另外一端接到PC机上 | ||

| + | #将SDRAM Board插入SDRAM接口 | ||

| + | #Download the program | ||

| + | |||

| + | |- | ||

| + | | style="text-align: center;" | | ||

| + | '''Phenomena''' | ||

| + | |||

| + | | | ||

| + | * 打开串口调试助手,波特率设置为9600 | ||

| + | * 发送一个任意键盘字母或数字在串口调试助手显示 | ||

| + | |||

| + | | | ||

| + | * 打开串口调试助手,波特率设置为9600 | ||

| + | * 发送一个任意数字会在数码管上显示 | ||

| + | |||

| + | | | ||

| + | * 在Nios II软件的Console栏,先发送任意字,再发送“t”串口会检测到“t” | ||

| + | * 发送“v”关闭串口 | ||

| + | |- | ||

| + | | <p align="center"> '''实验视频'''</p> | ||

| + | | <p align="center">[[File:video-logo.png|30px|link=Altera-Test-16-UART-Verilog]] </p> | ||

| + | | <p align="center">[[File:video-logo.png|30px|link=Altera-Test-16-UART-VHDL]] </p> | ||

| + | | <p align="center">[[File:video-logo.png|30px|link=Altera-Test-16-UART-NIOS]] </p> | ||

| + | |} | ||

| + | <br /> | ||

| + | |||

| + | === I2C EEPROM实验 === | ||

| + | <br /> | ||

| + | {| class="tabSty_1" width="96%" border="1" | ||

| + | |- | ||

| + | ! | | ||

| + | <span style="font-weight: normal;">Language</span> | ||

| + | |||

| + | ! | <span style="font-weight: normal;">Verilog</span> | ||

| + | ! | <span style="font-weight: normal;">VHDL</span> | ||

| + | ! | <span style="font-weight: normal;">Nios II C</span> | ||

| + | |- | ||

| + | | style="text-align: center;" | | ||

| + | '''Sample Program Name''' | ||

| + | |||

| + | | colspan="3" style="text-align: center;" | AT24CXX | ||

| + | |- | ||

| + | | style="text-align: center;" | | ||

| + | '''Steps''' | ||

| + | |||

| + | | colspan="2" | | ||

| + | #将AT24CXX EEPROM Board插入8I/Os_1 | ||

| + | #将8 SEG LED Board插入16I/Os_2 | ||

| + | #Download the program | ||

| + | |||

| + | | | ||

| + | #将AT24CXX EEPROM Board插入8I/Os_1 | ||

| + | #将8 SEG LED Board插入16I/Os_2 | ||

| + | #将SDRAM Board插入SDRAM接口 | ||

| + | #Download the program | ||

| + | |||

| + | |- | ||

| + | | style="text-align: center;" | | ||

| + | '''Phenomena''' | ||

| + | |||

| + | | colspan="2" | | ||

| + | *有两个数码管显示,其中的一个显示SDRAM_L的3,5,7,9管脚对AT24CXX中写入的数据,另外一个显示对从AT24CXX读到的数据 | ||

| + | *先用跳线帽短接SDRAM_R的5,6脚,再拔掉5,6脚跳线帽,短接SDRAM_R的3,4脚,则对应的写入的数据会先写入到AT24CXX然后被读出来显示在数码管上 | ||

| + | |||

| + | | | ||

| + | * LED显示一个一个加 | ||

| + | |- | ||

| + | | style="text-align: center;" | | ||

| + | 备注 | ||

| + | |||

| + | | colspan="2" | | ||

| + | *程序中SDRAM_L的3,5,7,9号管脚初始状态设置为上拉输入高电平,SDRAM_L的4,6,8,10管脚为输出低电平,可以通过跳线帽短接3与4,5与6,7与8,9与10设置写入的数据 | ||

| + | | | ||

| + | | ||

| + | |- | ||

| + | | <p align="center"> '''实验视频'''</p> | ||

| + | | colspan="2" | <p align="center">[[File:video-logo.png|30px|link=Altera-Test-17-AT24CXX-Verilog_VHDL]] </p> | ||

| + | | <p align="center">[[File:video-logo.png|30px|link=Altera-Test-17-AT24CXX-NIOS]] </p> | ||

| + | |} | ||

| + | <br /> | ||

| + | |||

| + | === AT45DB实验 === | ||

| + | <br /> | ||

| + | {| class="tabSty_1" width="96%" border="1" | ||

| + | |- | ||

| + | ! | | ||

| + | <span style="font-weight: normal;">Language</span> | ||

| + | |||

| + | ! | <span style="font-weight: normal;">Verilog</span> | ||

| + | ! | <span style="font-weight: normal;">VHDL</span> | ||

| + | ! | <span style="font-weight: normal;">Nios II C</span> | ||

| + | |- | ||

| + | | style="text-align: center;" | | ||

| + | '''Sample Program Name''' | ||

| + | |||

| + | | style="text-align: center;" | —— | ||

| + | | style="text-align: center;" | —— | ||

| + | | style="text-align: center;" | AT45DBXX<br/> | ||

| + | |- | ||

| + | | style="text-align: center;" | | ||

| + | '''Steps''' | ||

| + | |||

| + | | | ||

| + | | | ||

| + | | | ||

| + | #将AT45DBXX DataFlash Board插入8I/Os_1 | ||

| + | #将SDRAM Board插入SDRAM接口 | ||

| + | |||

| + | |- | ||

| + | | style="text-align: center;" | | ||

| + | '''Phenomena''' | ||

| + | |||

| + | | | ||

| + | | | ||

| + | | | ||

| + | * LED显示一个一个加 | ||

| + | |||

| + | |} | ||

| + | |||

| + | === PCF8563 时钟实验 === | ||

| + | <br /> | ||

| + | {| class="tabSty_1" width="96%" border="1" | ||

| + | |- | ||

| + | ! | | ||

| + | <span style="font-weight: normal;">Language</span> | ||

| + | |||

| + | ! | <span style="font-weight: normal;">Verilog</span> | ||

| + | ! | <span style="font-weight: normal;">VHDL</span> | ||

| + | ! | <span style="font-weight: normal;">Nios II C</span> | ||

| + | |- | ||

| + | | style="text-align: center;" | | ||

| + | '''Sample Program Name''' | ||

| + | |||

| + | | style="text-align: center;" | —— | ||

| + | | style="text-align: center;" | —— | ||

| + | | style="text-align: center;" | PCF8563<br/> | ||

| + | |- | ||

| + | | style="text-align: center;" | | ||

| + | '''Steps''' | ||

| + | |||

| + | | | ||

| + | | | ||

| + | | | ||

| + | #将PCF8563 RTC Board插入8I/Os_1 | ||

| + | #将SDRAM Board插入SDRAM接口 | ||

| + | |||

| + | |- | ||

| + | | style="text-align: center;" | | ||

| + | '''Phenomena''' | ||

| + | |||

| + | | | ||

| + | | | ||

| + | | | ||

| + | * Nios II软件的Console栏显示时间 | ||

| + | |||

| + | |} | ||

| + | |||

| + | === USB转FIFO实验 === | ||

| + | <br /> | ||

| + | {| class="tabSty_1" width="96%" border="1" | ||

| + | |- | ||

| + | ! | | ||

| + | <span style="font-weight: normal;">Language</span> | ||

| + | |||

| + | ! | <span style="font-weight: normal;">Verilog</span> | ||

| + | ! | <span style="font-weight: normal;">VHDL</span> | ||

| + | ! | <span style="font-weight: normal;">Nios II C</span> | ||

| + | |- | ||

| + | | style="text-align: center;" | | ||

| + | '''Sample Program Name''' | ||

| + | |||

| + | | style="text-align: center;" | —— | ||

| + | | style="text-align: center;" | —— | ||

| + | | style="text-align: center;" | FT245<br/> | ||

| + | |- | ||

| + | | style="text-align: center;" | | ||

| + | '''Steps''' | ||

| + | |||

| + | | | ||

| + | | | ||

| + | | | ||

| + | #将FT245 USB FIFO Board插入16I/Os_2,并把它的另外一端接到PC机上 | ||

| + | #将SDRAM Board插入SDRAM接口 | ||

| + | #Download the program | ||

| + | |||

| + | |- | ||

| + | | style="text-align: center;" | | ||

| + | '''Phenomena''' | ||

| + | |||

| + | | | ||

| + | | | ||

| + | | | ||

| + | * 在串口助手发送任意一个数,串口助手显示出来 | ||

| + | |||

| + | |} | ||

== References == | == References == | ||

<references /> | <references /> | ||

Revision as of 10:05, 29 May 2015

Overview

- Design pricipal and user guide of OpenEP4CE10-C, one of FPGA Altera serial board[1], are in the present document, for helping you quick start your FPGA development.

Hardware Design

- This chapter mainly about the basic idea of CoreEP4CE10's hardware design. Go with you to witness how a EP4CE10F17C8N chip becomes CoreEP4CE10 board.

- There are voltage regulator AMS1117, serial FLASH memory EPCS16, crystal oscillator, JTAG interface, LEDs, buttons, etc., beside main FPGA. See product description What's On Board. Then, how and why do the devices connect together? What are their functions?

Framework of the Circuit

Power Supply Circuit

- Power Supply Circuit is the basic circuit for CoreEP4CE10's normal operation. You can find voltage supplies details from the File:Cyclone-IV-Device-Handbook.pdf. Noting that EP4CE10F17C8N requires 1.0V/1.2V for Internal core supply voltage (VCCINT) and PLL digital power supply (VCCD_PLL), requires 2.5V for PLL analog power supply (VCCA). Then I/O banks power supply VCCO can be connected to 1.2, 1.5, 1.8, 2.5, 3.0, 3.3 to supply each area with different voltage standards. So for normal operation, the power supply of the board is designed for converting input voltage 5V to multiple voltages 3.3V, 2.5V, 1.2V. Meanwhile, a PWR LED is connected to 3.3V output, to meet the needs of checking power operation status. The schematic of the circuit:

| Pin Name | Description |

|---|---|

| VCC5 | 5V supply voltage, External Input |

| VCC33 | 3.3V voltage, converted from AMS1117-3.3, is generally used to supply the voltage of clock, configure circuit, special features pin high, etc. |

| VCC25 | 2.5V voltage, converted from AMS1117-2.5, is generally used to supply the voltage of VCCA. |

| VCC12 | 1.2V voltage, converted from AMS1117-1.2, is generally used to supply the voltage of VCCINT, VCC_PLL, etc. |

Clock Circuit

- The best solution of FPGA clock circuit is: A main clock, which is driven by dedicated global clock input(GCLK), controls each timing device of the design. Try to use global clock at any design. The FPGA has dedicated global clock pin, which is connected to each register of the device. The shortest time span of GCLK can supply is used for delay. We use a global clock interface CLK in our design, because it is single clock interface, we consider the use of active crystal clock as an external clock source. A 50MHz crystal oscillator on board is used for supply accurate clock. The schematic of the circuit:

- The best solution of FPGA clock circuit is: A main clock, which is driven by dedicated global clock input(GCLK), controls each timing device of the design. Try to use global clock at any design. The FPGA has dedicated global clock pin, which is connected to each register of the device. The shortest time span of GCLK can supply is used for delay. We use a global clock interface CLK in our design, because it is single clock interface, we consider the use of active crystal clock as an external clock source. A 50MHz crystal oscillator on board is used for supply accurate clock. The schematic of the circuit:

| Pin Name | Description |

|---|---|

| CLK | Clock input |

Reset Circuit

- The Reset Circuit contains RST Reset Circuit and nCONFIG Reconfigure Circuit. RST reset Circuit is a RC reset Circuit with RESET button switch, which is pressed to generate a Reset-signal, active-low. While nCONFIG Reset Circuit is triggered by nCONFIG key. FPGA will be reconfigured without reboot when the nCONFIG key is pressed. The schematic of the circuit:

| Pin Name | Description |

|---|---|

| RESET | Active-low Reset |

| nCONFIG | Active-low Reset, FPGA will be reconfigured, as soon as PROG_B pin restores to high level |

Configuration/Programming Interface

- Configuration is also known as loading and download. It is a process of FPGA programming. FPGA reconfigured at each reboot is a feature of SRAM-based FPGA. Within the FPGA, many programmable multiplexers, logic, interconnect nodes and RAM initialization, etc. are controlled by configuration data, which is stored in FPGA RAM.

- The configured data of FPGA can be downloaded to target device with 3 methods, FPGA Active, FPGA Passive and JTAG, according to the role played in Configure Circuit. JTAG is an industry-standard interface. Usually All Altera FPGA can be configured via JTAG commands. Meanwhile, JTAG has more priority than other configuration method. Of course this board provides JTAG interface. The schematic of the circuit:

- User can use dedicated Altera programmer USB Blaster to debug and program. File to be programmed to EPCS should be converted to .jic file by Quartus. That is, Set it as "JTAG Indirect Configuration File" and then uses the JTAG interface to program the EPCS device. See File:Cyclone-IV-Device-Handbook.pdf.

| Pin Name | Description |

|---|---|

| TDI | Test data input. Serial input pin for instructions as well as test and programming data. |

| TDO | Test data output. Serial data output pin for instructions as well as test and programming data. |

| TMS | Test mode select. Input pin that provides the control signal to determine the transitions of the TAP controller state machine. |

| TCK | Test clock input. The clock input to the BST circuitry. |

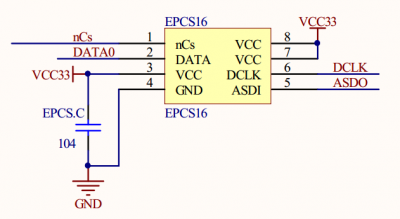

Configuration Circuit

- An EPCS16, Altera EPCS serial flash devices, is connected to the FPGA for keeping the data without power supplied. EPCS16 is one of advanced Configuration Device, 16Mbit density. It supports high capacity single configuration of FPGA. It also support in-system programming by JTAG interface. The schematic of the circuit:

LED Circuit

- 4 LEDs onboard. Each LED is driven via one of the FPGA pins. When a low level inputs to LED pin, the corresponding LED turns on. The schematic of the circuit:

Extention Board interface

- Series of Open boards designed by Waveshare are based on Core-Extension-Separated idea. On the one hand, users can easily design extension circuit according to their needs, On the other hand, the interfaces of core board and extension board are fully considered about the compatible to other FPGA boards, make update easier.

Basic Operation

Power Up And Download

- Power up CoreEP4CE10 with 5V supply. That is, connect corresponding 5V pin and GND pin to a 5V supply by jumper wires. Then the PWR_LED will light up in usual. The onboard JTAG interface is used for programming with dedicated programmer USB Blaster, as shown in the following figure:

- If you use CoreEP4CE10 and OpenEP4CE10-C together, just connect the core board to the mother board, and plug a 5V adapter directly without any jumper wire. Turn the switch on to power up.

- Run the software Quartus II to download the Verilog and VHDL demo:

General Download Process

- 1. Copy the Nios II processors (Quartus II projects) to your computer, which are located in ".\nios\Quartus II Project".

- 2. Launch Nios II IDE

- 1) Create a new Nios II project.

- 2) Config the Nios processor by specifying the PTF file directory on the "Select Target Hardware" section. The PTF file directory depends on where you placed the Nios II processors in step 1.

- 3) Copy the corresponding c code in ".\nios\Nios II C Code" into the new project.

- 4) Build the new Nios II project.

- 3. Connect the development board to the PC through a download cable.

- 4. Back to the Nios II IDE

- 1) Download the Nios II processor to the FPGA, select"Tools->Quaters II Programmer" to download the sof file.

- 2) Run the Nios II project (right click the makefile, select "Run ->Run As->2 Nios II Hardware", it may takes several minutes). When download completed, the demo code should starts to run automatically.

Quick Start

- All the following demo require power supply. Verilog, VHDL and NIOS are used in the following demos, please download the corresponding one.

- An OpenEP4CE10-C development board is used for demonstration, other Altera boards are similar to it. If there are differences on any example, they will be special explained.

- All the following demo require power supply. Verilog, VHDL and NIOS are used in the following demos, please download the corresponding one.

Light Up LEDs

Language |

Verilog |

VHDL |

Nios II C |

|---|---|---|---|

Sample Program Name |

LED |

LED_hello_world | |

Steps |

| ||

Phenomena |

|

| |

实验视频 |

|||

控制摇杆JOYSTICK实验

|

Language |

Verilog |

VHDL |

Nios II C |

|---|---|---|---|

Sample Program Name |

JOYSTICK | ||

Steps |

| ||

Phenomena |

| ||

实验视频 |

|||

8 Push Buttons按键实验

|

Language |

Verilog |

VHDL |

Nios II C |

|---|---|---|---|

Sample Program Name |

8 Push Buttons |

—— | |

Steps |

|

||

Phenomena |

|

||

实验视频 |

-- | ||

8 LEG LED Board数码管实验

|

Language |

Verilog |

VHDL |

Nios II C |

|---|---|---|---|

Sample Program Name |

8 SEG LED Board |

—— | |

Steps |

|

||

Phenomena |

|

||

实验视频 |

-- | ||

4x4 Keypad矩阵键盘控制数码管实验

|

Language |

Verilog | VHDL | Nios II C |

|---|---|---|---|

|

Sample Program Name |

4x4 Keypad | ||

|

Steps |

|

|

|

|

Phenomena |

|

|

|

实验视频 |

|||

DS18B20温度传感器实验

|

Language |

Verilog | VHDL | Nios II C |

|---|---|---|---|

Sample Program Name |

DS18B20 | ||

|

Steps |

|

|

|

|

Phenomena |

|

|

|

蜂鸣器实验

|

Language |

Verilog |

VHDL |

Nios II C |

|---|---|---|---|

Sample Program Name |

Buzzer/PWM |

—— | |

Steps |

|

||

Phenomena |

|

||

PS/2键盘实验

|

Language |

Verilog | VHDL | Nios II C |

|---|---|---|---|

|

Sample Program Name |

PS2 | ||

|

Steps |

|

| |

|

Phenomena |

|

| |

实验视频 |

|||

VGA显示实验

|

Language |

Verilog | VHDL | Nios II C |

|---|---|---|---|

|

Sample Program Name |

VGA_color | VGA | —— |

|

Steps |

|

||

|

Phenomena |

|

||

实验视频 |

-- | ||

字符LCD1602实验

|

Language |

Verilog |

VHDL |

Nios II C |

|---|---|---|---|

Sample Program Name |

LCD1602 |

—— | |

Steps |

|

||

Phenomena |

|

||

点阵LCD12864实验

|

Language |

Verilog | VHDL | Nios II C |

|---|---|---|---|

|

Sample Program Name |

LCD12864 | —— | —— |

|

Steps |

|

||

|

Phenomena |

|

3.2寸LCD屏显示触摸实验

|

Language |

Verilog | VHDL | Nios II C |

|---|---|---|---|

|

Sample Program Name |

—— | —— | LCD32 |

|

Steps |

| ||

|

Phenomena |

|

USB通信实验

|

Language |

Verilog | VHDL | Nios II C |

|---|---|---|---|

|

Sample Program Name |

—— | USB | —— |

|

Steps |

|

||

|

Phenomena |

|

|

|

|

备注 |

|

|

|

实验视频 |

-- |

-- |

SD-Card实验

|

Language |

Verilog | VHDL | Nios II C |

|---|---|---|---|

|

Sample Program Name |

—— | —— | SD-Card |

|

Steps |

| ||

|

Phenomena |

|

|

Ethernet以太网口通信实验

|

Language |

Verilog | VHDL | Nios II C |

|---|---|---|---|

|

Sample Program Name |

—— | —— | ENC28J60 |

|

Steps |

| ||

|

Phenomena |

|

UART串口通信实验

|

Language |

Verilog | VHDL | Nios II C |

|---|---|---|---|

|

Sample Program Name |

UART | ||

|

Steps |

|

|

|

|

Phenomena |

|

|

|

实验视频 |

|||

I2C EEPROM实验

|

Language |

Verilog | VHDL | Nios II C |

|---|---|---|---|

|

Sample Program Name |

AT24CXX | ||

|

Steps |

|

| |

|

Phenomena |

|

| |

|

备注 |

|

| |

实验视频 |

|||

AT45DB实验

|

Language |

Verilog | VHDL | Nios II C |

|---|---|---|---|

|

Sample Program Name |

—— | —— | AT45DBXX |

|

Steps |

| ||

|

Phenomena |

|

PCF8563 时钟实验

|

Language |

Verilog | VHDL | Nios II C |

|---|---|---|---|

|

Sample Program Name |

—— | —— | PCF8563 |

|

Steps |

| ||

|

Phenomena |

|

USB转FIFO实验

|

Language |

Verilog | VHDL | Nios II C |

|---|---|---|---|

|

Sample Program Name |

—— | —— | FT245 |

|

Steps |

| ||

|

Phenomena |

|